Programmation des FPGA de chez Xilinx:

Introduction: La configuration du circuit est mémorisée sur la couche réseau SRAM et stockée dans une ROM externe. Un dispositif interne permet à chaque mise sous tension de charger la SRAM interne à partir de la ROM. Ainsi on conçoit aisément qu'un même circuit puisse être exploité successivement avec des ROM différentes puisque sa programmation interne n'est jamais définitive. On voit tout le parti que l'on peut tirer de cette souplesse en particulier lors d'une phase de mise au point. Une erreur n'est pas rédhibitoire, mais peut aisément être réparée.Technique de programmation des FPGA: Les circuits FPGA ne possèdent pas de programme résident. A chaque mise sous tension, il est nécessaire de les configurer. Leur configuration permet d'établir des interconnexions entre les CLB et IOB. Pour cela, ils disposent d'une RAM interne dans laquelle sera écrit le fichier de configuration. Le format des données du fichier de configuration est produit automatiquement par le logiciel de développement sous forme d'un ensemble de bits organisés en champs de données. Le FPGA dispose de quatre modes de chargement et de trois broches M0, M1, M2 lesquelles définissent les différents modes comme l'indique le tableau ci-dessous. Ces modes définissent les différentes méthodes pour envoyer le fichier de configuration vers le circuit FPGA, selon deux approches complémentaires :

- configuration automatique, le circuit FPGA est autonome,

- configuration externe, l'intervention d'un opérateur est nécessaire.

- M0 M1 M2 Mode sélectionné

- 0 0 0 maître série

- 0 0 1 maître parallèle bas

- 0 1 1 maître parallèle haut

- 1 0 1 périphérique

- 1 1 1 esclave série

- Mode maître série:

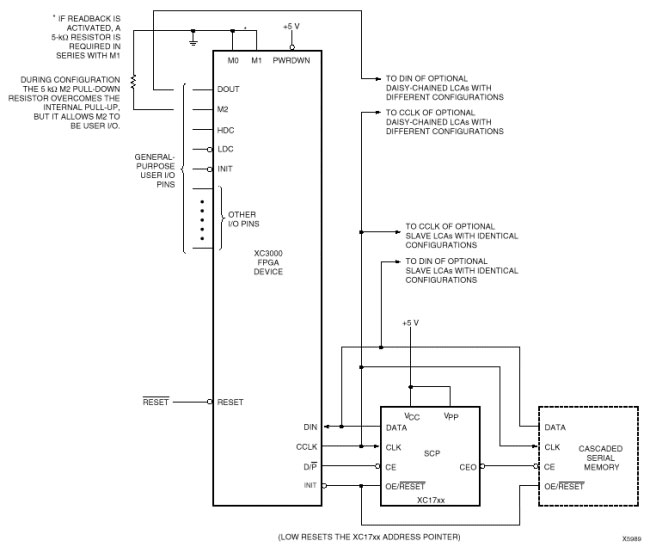

Le mode maître série utilise une mémoire à accès série de type registre à décalage commercialisée par le fabricant Xilinx. Le programme est préalablement chargé par le système de développement utilisé pour le circuit FPGA. Le FPGA génère tous les signaux de dialogue nécessaires pour la copie du contenu de la PROM dans sa RAM interne, lorsque la copie est terminée, il bascule le signal DONE pour le signaler au circuit. Comme nous pouvons le remarquer sur la figure, une seule PROM peut configurer plusieurs circuits FPGA avec la même configuration ou plusieurs PROM peuvent configurer plusieurs FPGA en chaîne où le premier des circuits FPGA est le maître et génère l'horloge. Les données en provenance des PROM sont envoyées aux autres circuits FPGA par la sortie DOUT de ce premier.

On dispose aussi d'un mode maître-parallèle où le FPGA est relié en parallèle à une EPROM classique, de même qu'un mode passif type périphérique dans lequel le FPGA est considéré comme un périphérique de µP et peut-être configuré à partir de celui-ci.

- Mode esclave: Dans ce mode, le programme de configuration peut être envoyé à partir d'un PC, d'une station de travail ou à partir d'un autre circuit FPGA. Le circuit FPGA maître peut être interfacé à une mémoire en mode parallèle ou série sans apporter aucune modification au niveau du câblage des circuits FPGA esclaves. C'est souvent le mode exploité pour la mise au point d'une configuration.

Programmation des FPGA: On commence par décrire le design soit en utilisant un language de description matériel (tel VHDL, Verilog, ABEL,...) soit en rentrant directement le schématique. Le synthétiseur va générer la netlist, ensuite il faudra placer tous ces composants (si c'est possible, en effet, certains FPGA ne permettent pas d'émuler des Latchs) dans un FPGA et effectuer le routage entre les différentes cellules logiques. Au terme de ces étapes, le synthétiseur aura générer le bitstream qui sera prêt à être envoyer vers le FPGA. C'est seulement à ce moement là que la programmation proprement dite pourra avoir lieu.